数电是一门专业基础课,讲的是数字电路,所以在数电的世界里只有0和1。数电的直接应用是FPGA,而我认为数电更像是一门为其他课程打基础的课程。比如数电的直接服务对象——微机原理。数电本身的一些东西学了之后只是知道了有这么一个东西,但是在微机原理中,你会看到这些数字电路的直接使用,为他们的奇妙作用而惊叹。当然啦,对于外人来说,感觉这个世界还有自己的电脑竟然全是靠着这些0,1来构成的,感觉非常的神奇@曾某。

数制 & 逻辑代数

二进制,八进制,十进制,十六进制。用的最多的就是十六进制和十进制。BCD码更像是表示码,有点c语言中char的感觉哈哈。

数电引入了逻辑代数,在简单的电路分析中会感觉逻辑代数很累赘,不如自己直接分析逻辑来的舒服。但是,一门学科要成为科学,就必定要用数学公式来表达一切。在复杂的数字电路中,逻辑表达式在电路分析方面显得极其有用。

逻辑代数中还告诉我们有很多种方法来表达一个数字电路的输入输出关系。

- 真值表:枚举所有可能情况,主要用于设计电路的时候使用。

- 逻辑表达式:数学公式表达结果,主要用于正向运算。

卡诺图:用于简化逻辑表达式。

波形图:常用于表示时序,主要用在异步时序电路中。

基本逻辑门电路

主要的制作材料为TTL和COMOS。BJT,MOS工作于截至区和饱和区。

特殊的门电路

- 传输门

控制门两端是否相连,双向导通。

- OD门

需要外接电阻和电源,最大的特点是可以实现线与功能。

- 三态门

通过EN来控制门是否工作,工作时单向导通,不工作时高阻。主要用于微机中的总线接口处。

门电路关心的参数

- 电平匹配

- 噪声容限

- 传输延时(多级联的时候竞争冒险很严重)

- 扇入扇出数:能带动多少门。(带载能力)

组合逻辑电路

编码器,译码器,数据选择器,数值比较器,运算电路(半加器,全加器,超前进位加法器)

主要功能每个电路都各有各的特点,在微机中用的最多的就是译码器,用于选中AB上选择的外设。

组合电路里主要的计算就是依靠逻辑表达式了,感受到了数学公式的强大和巧妙之处,我们没有必要推每一个门电路的输入输出状态再推到最终输出,直接依靠数学公式就可以解决了。

时序逻辑电路

为什么叫时序电路呢?主要就是引入了时序电路的基本单元——触发器。

锁存器 & 触发器

- 锁存器

锁存器由双稳态电路组成,中间用E做控制电路,控制使能,一般来说在E为高电平的时候使能。触发器能“记忆”前一个状态,主要功劳就是双稳态电路,双稳态电路是一种将输出引回到输入端的电路,达到稳态效果。

- 触发器

触发器基本电路由两个锁存器组成,外部特性就是触发器对上升下降沿敏感,而锁存器对高低电平敏感。

锁存器具体怎么组成触发器的呢?大致的原理就是两个级联,电平信号在两个触发器只有在高低电平转换的一瞬间可以同时使能一下。简单来说就是……趁锁存器不注意给他信号。

时序电路设计和分析

时序电路分为同步和异步时序电路,主要区别在于电路中所有的触发器的时钟信号是不是同一个。

同步时序电路

分析主要通过激励方程,触发器特性方程(状态方程)来得到输出方程。分析还是比较容易的,因为有数学公式。

设计呢主要就是逆向设计了,根据要求画出真值表,简化状态,编码,选择触发器,最后检查自启动。

异步时序电路

异步时序电路的分析一般来说分析都是使用时序波形图来分析,因为时钟公式不一样,这样运用逻辑表达式来计算的时候就不是很方便。

存储器

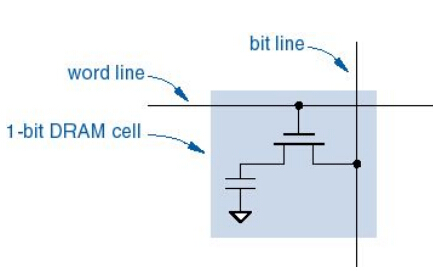

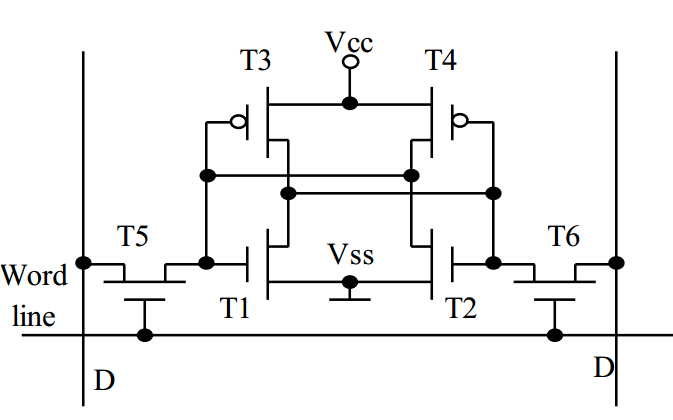

按材质分分为DRAM和SRAM。

DRAM由于是用电容来储存的,电容会漏电,所以需要刷新(读出数据之后再把数据写入)。

还有一个学到的东西就是,终于知道为什么金条上的RAM芯片是8个了——8个数据位,为了并行读取数据。

FPGA

不算是考试学习的重点,但是了解下还是挺有意思的。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列。编程之后的效果就是能够在FPGA内部产生大量的门电路。

FPGA最大的特点就是他是使用门电路来实现功能的。程序的运行是跟着时钟频率走的。反观单片机,作为一个微机,单片机所有的数据处理都由CPU来处理,为了能实现一些操作的并发执行,还要分时间片处理每一个进程。从实质上来讲,算是”假“的并发执行。然而FPGA,由于所有的门电路操作都是由时钟驱动的,达到了真正的并发执行。这就是FPGA厉害的地方——强大的并发执行能力。难怪现在说的硬件人工智能化都是在说FPGA。

波形产生电路

主要就是555定时器组成单稳态触发器、施密特触发器和多谐振荡器。